# ディジタルフィルタの回路構成

本章ではディジタルフィルタの基本構成,標準的な構成法,マルチレートフィルタの構成法について述べる。

# 7.1 回路構成の基本方針

#### 7.1.1 構成要素

線形シフト不変システムは第1章でも述べたように,加算器,乗算器,遅延器を要素として構成される。

#### 7.1.2 回路構成のポイント

- 1. 素子の数が少ないこと。

- 2. 素子感度が低いこと。

- 3. 回路内部で発生する量子化誤差の増幅が小さいこと。すなわち,フィルタ出力における雑音が小さいこと。

- 4. ハードウェアまたはディジタルシグナルプロセッサ (DSP)のプログラム 化が容易であること。すなわち,回路に規則性があること,同じモジュールが繰り返して使用できること。

- 5. 乗算器の乗数の大きさがばらつかないこと。固定小数点の場合に重要である。

### 7.1.3 回路構成の基本的な考え方

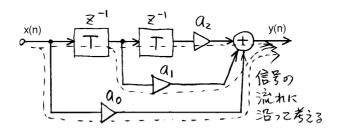

1. 分子はフィードフォワード(順路)で構成される。

$$y(n) = a_0 x(n) + a_1 x(n-1) + a_2 x(n-2)$$

(7.1)

$$H_1(z) = a_0 + a_1 z^{-1} + a_2 z^{-2} (7.2)$$

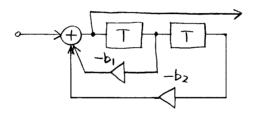

2. 分母はフィードバック(帰還路)で構成される。

$$y(n) = x(n) - b_1 y(n-1) - b_2 y(n-2)$$

(7.3)

$$H_2(z) = \frac{1}{1 + b_1 z^{-1} + b_2 z^{-2}} \tag{7.4}$$

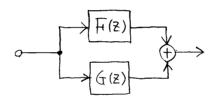

3. 回路の縦続構成は伝達関数の積となる。

$$H_3(z) = F(z)G(z) \tag{7.5}$$

4. 回路の並列構成は伝達関数の和となる。

$$H_4(z) = F(z) + G(z)$$

(7.6)

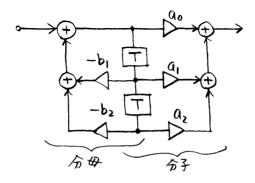

5. 最少素子構成とする。伝達関数の自由度と同じ自由度を有する回路構成とする。

$$y(n) = a_0 x(n) + a_1 x(n-1) + a_2 x(n-2)$$

$$- b_1 y(n-1) - b_2 y(n-2)$$

(7.7)

$$H_5(z) = \frac{a_0 + a_1 z^{-1} + a_2 z^{-2}}{1 + b_1 z^{-1} + b_2 z^{-2}}$$

(7.8)

これらに対応する具体例を図 7.1~図 7.5 に示す。 図 7.5 では,分子と分母の

図 7.1 フィードフォワードの構成

$z^{-1}$  を共用している。独立な係数が 5 個あるため,乗算器は 5 個必要である。この回路における入出力関係は入力側の加算器の出力を w(n) として,次のように表される.伝達関数はこの方程式を z 変換し,W(z) を消去することにより

図 7.2 フィードバックの構成

図 7.3 縦続構成

図 7.4 並列構成

図 7.5 2次 IIR フィルタの最小構成

求められる.

$$w(n) = x(n) - b_1 w(n-1) - b_2 w(n-2)$$

(7.9)

$$y(n) = a_0 w(n) + a_1 w(n-1) + a_2 w(n-2)$$

(7.10)

# 7.2 伝達関数を直接表現する回路形式

#### 7.2.1 直接構成(高次多項式)

$$y(n) = a_0 x(n) + a_1 x(n-1) + \dots + a_{M-1} x(n-M+1)$$

$$- b_1 y(n-1) - \dots - b_{N-1} y(n-N+1)$$

$$H(z) = \frac{a_0 + a_1 z^{-1} + \dots + a_{M-1} z^{-M+1}}{1 + b_1 z^{-1} + \dots + b_{N-1} z^{-N+1}}$$

$$(7.11)$$

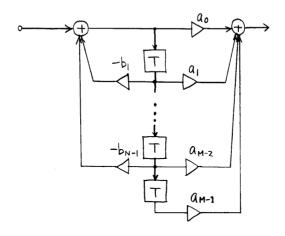

図 7.6 においては、分子を入力側、分母を出力側に配置することもできる。伝

図 7.6 直接形構成

達関数が分母のみ,分子のみ(FIR フィルタに相当)の場合は,一方の部分を取り除けばよい。この回路における入出力関係も図??の場合と同様に,入力側の加算器出力をw(n) として表すことができる。伝達関数はz変換後にW(z)を

消去することにより求められる.

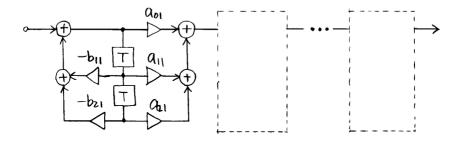

# 7.2.2 縦続構成 - 2次因数分解

$$H(z) = \frac{\prod_{i=1}^{N} (a_{0i} + a_{1i}z^{-1} + a_{2i}z^{-2})}{\prod_{j=1}^{M} (1 + b_{1j}z^{-1} + b_{2j}z^{-2})}$$

(7.13)

2次の伝達関数を  $H_i(z)$  とすると,

$$H(z) = \prod_{i=1}^{K} H_i(z), \ K = \max\{M, N\}$$

(7.14)

分子,分母で次数が不足する場合は,

分子:

$$a_{0i} = 1$$

,  $a_{1i} = 0$ ,  $a_{2i} = 0$  (7.15)

分母:

$$b_{1i} = 0, b_{2i} = 0$$

(7.16)

とおく。

図 7.7 2 次回路の縦続構成。 2 次回路では分母が入力側に配置されている。

#### 2次の縦続構成は,

- 1. 回路構成に規則性があり, ハードウェア化や DSP のプログラム化に適している。

- 2. 量子化誤差の影響も比較的少ない。

- 3. 伝達関数の係数と乗算器の乗数が直接対応する。

図 7.8 分子を入力側に配置した 2 次 IIR の構成

といった、利点があり、実用的にも多く用いられる回路形式である。

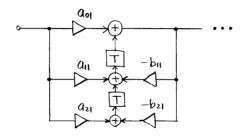

#### 7.2.3 部分分数展開による並列構成

$$H(z) = \alpha + \sum_{i=1}^{M} \frac{a_{oi} + a_{1i}}{1 + b_{1i}z^{-1} + b_{2i}z^{-2}}$$

(7.17)

図 7.9 伝達関数の部分分数展開による並列構成

この回路形式は規則性は若干失われるが,量子化誤差の影響も比較的少ない。

2次縦続構成に比べて零点と極の組み合わせ,及び2次回路の並べ順を最適化 する必要はない、という利点はある。

#### 7.2.4 連分数展開によるはしご形構成

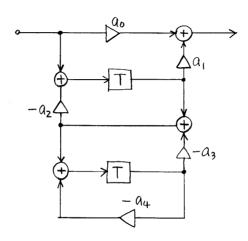

$$H(z) = a_0 + \frac{a_1 z^{-1}}{1 + \frac{a_2 z^{-1}}{1 + a_4 z^{-1}}}$$

$$(7.18)$$

図 7.10 伝達関数の連分数展開によるはしご形構成

この回路形式は素子感度は低くできるが、回路の規則性が低いという問題が ある。

#### 7.2.5 格子形回路

#### [1] 全域通過フィルタ

$$H(z) = \frac{a_0 + a_1 z^{-1} + z^{-2}}{1 + a_1 z^{-1} + a_0 z^{-2}}$$

(7.19)

$$|H(e^{j\omega})| = 1, -\pi \le \omega T \le \pi \tag{7.20}$$

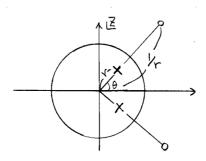

この伝達関数の極と零点は次のようになり, z 平面では図 7.11 のように鏡像関

係となる。

極

$$re^{\pm j\theta}, |r| < 1$$

(7.21)

零点

$$r^{-1}e^{\pm j\theta}$$

(7.22)

図 7.11 全域通過フィルタの零点, 極分布

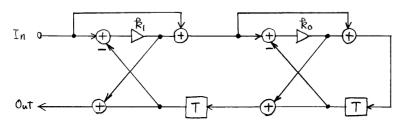

伝達関数の係数の自由度は  $a_0$  と  $a_1$  の 2 個である。従って,遅延器 2 個,乗算器 2 個で構成できる。この回路は図 7.12 に示すように格子形となる。加算器は 6 個必要となる。 $k_0$  ,  $k_1$  を用いた伝達関数は次のように表される。

図 7.12 格子形回路による全域通過フィルタの構成

$$H(z) = \frac{k_1 + k_0(1+k_1)z^{-1} + z^{-2}}{1 + k_0(1+k_1)z^{-1} + k_1z^{-2}}$$

(7.23)

$$k_1 = a_0 \tag{7.24}$$

$$k_0 = \frac{a_1}{1 + k_1} \tag{7.25}$$

2次縦続回路では,乗算器4個,加算器4個,遅延器2個で構成される。こ

こで,加算器は2入力を1個と数える。格子形回路では,上で述べたように乗算器2個,加算器6個,遅延器2個で実現できる。ハードウェアやプログラムで乗算器の占める割合が高い場合には格子形回路が有効である。

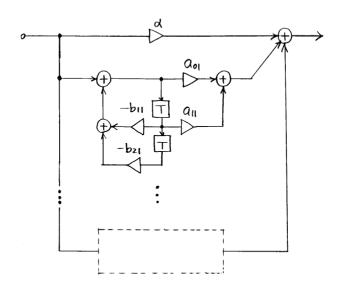

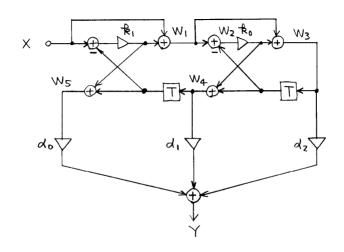

#### [2] 格子形回路による2次 HR フィルタの構成

さらに,一般の2次IIRフィルタに対する格子形回路は図7.13のようになる。 図7.5に比べて,乗算器と遅延器の数は等しいが,加算器は4個から8個に増 えている。素子感度は格子形回路の方が低い。

図 7.13 格子形回路による 2 次 HR フィルタの構成

#### 7.2.6 回路形式の比較

表 7.1 に各回路形式の比較を示す。最近の DSP は 32 ビット浮動小数点が主流になっており,音声,音響帯域では,素子感度や雑音特性よりも回路構成の規則性やモジュール化が重要となっている。しかし,より高い周波数帯域では,カスタム LSI が使われる場合も多く,できるだけ素子数やビット数を低減できる構成が望ましい。

| 性質    | 直接形     | 縦続形     | 並列形   | はしご形  | 格子形   |

|-------|---------|---------|-------|-------|-------|

| 素子感度  | IIR:高い/ | 少し高い    | 少し高い  | 低い    | 低い    |

|       | FIR:阻止  |         |       |       |       |

|       | 域で高い    |         |       |       |       |

| 出力雑音  | IIR:高い/ | IIR:低い/ | 低い    | 低い    | 低い    |

|       | FIR:低い  | FIR:高い  |       |       |       |

| 計算量   | 少ない     | 少ない     | 若干増える | 少ない   | 若干増える |

|       |         |         |       |       |       |

| 回路構造の | 積和演算    | 2次回路の   | やや不規則 | 規則性,モ | モジュール |

| 規則性   |         | モジュール   |       | ジュール化 | 化にやや不 |

|       |         | 化       |       | に不向き  | 向き    |

表 7.1 回路構成の比較

# 7.3 マルチレートフィルタ

ディジタルシステムでは複数の標本化周波数(レート)が使われる場合が多い。例えば、音響システムでは、国や方式によって音響信号の標本化周波数が異なる。また、周波数分割多重方式 (FDM) と時分割多重方式 (TDM) が混在するネットワークでは変換が必要である。さらに、標本化周波数を操作することにより、特性の改善や信号処理の効率化を図ることができる。

#### 7.3.1 レート変換フィルタ

#### [1] アップサンプリング

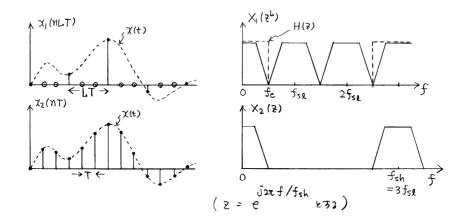

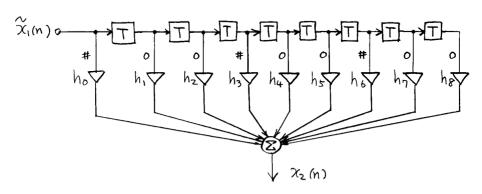

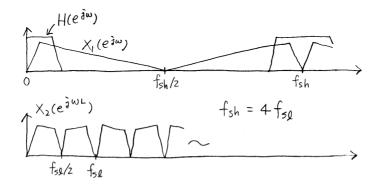

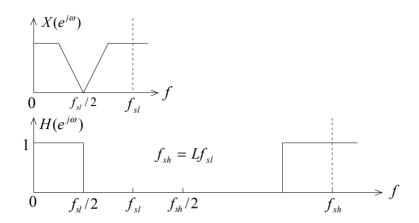

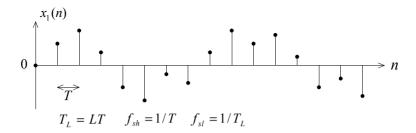

$f_{sl}$  で標本化された信号  $x_1(nLT)$  を  $f_{sh}=1/T=Lf_{sl}$  で標本化された信号  $x_2(nT)$  に変換する場合を考える。L=3 の場合の例を図 7.14 , 図 7.15 に示す。  $x_1(nLT)$  において,周波数特性をそのまま(定数倍は除く)に保って,標本 化周波数を  $f_{sh}=Lf_{sl}$  にするために,白丸の箇所に零のサンプルが挿入される。零内挿された信号  $\tilde{x}_1(nT)$  の周波数特性は  $x_1(nLT)$  と同じであるが,標本 化周波数は  $f_{sl}$  から  $f_{sh}=Lf_{sl}$  に変わっている。 $\tilde{x}_1(nT)$  を H(z) を伝達関数と

図 7.14 レート変換 (アップサンプリング) における時間信号と周波数特性の関係

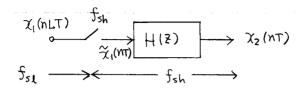

図 7.15 レート変換 (アップサンプリング)を行うフィルタ構成

するフィルタに入力する。H(z) は  $f_{sh}$  で動作するフィルタである。これにより, $f_{sl}$  、 $2f_{sl}$  を中心とした周波数成分を除去して, $X_2(z)$  を得る。波形では,零内挿のサンプルが元の波形に復元された  $x_2(nT)$  が得られる。この際,L 倍のスケーリングが必要である。

次に,H(z)を FIR フィルタ(直接形)で実現する例を図 7.16 に示す。この

図 7.16 レート変換 (アップサンプリング)を行う FIR フィルタ

回路において, $h_i$  の乗算器に入力する  $\tilde{x}_1(n-i)$  は L サンプル中 L-1 サンプルは零であるから,この部分は計算は必要ない。図中 # 印が非零サンプルであり,〇 印が零サンプルである。次のサンプル  $x_2(n+1)$  を計算するときは右へ 1 タップだけずれる。従って,出力  $x_2(n)$  を 1 サンプル計算するのに必要な乗算回数はフィルタ係数の数 N に対して Int[(N-1)/L]+1 である。ここで,Int[] は切り捨てによる整数化を行う演算とする。

# [2] ダウンサンプリング

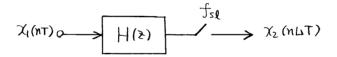

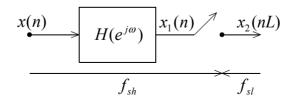

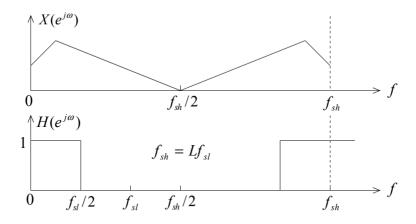

$f_{sh}$  で標本化された信号  $x_1(nT)$  を  $f_{sl}=f_{sh}/L$  でダウンサンプリングする場合を考える。 $x_1(nT)$  の周波数特性  $X(e^{j\omega})$  が  $|f|< f_s/2$  の範囲に広がっている場合は,帯域制限フィルタ H(z) を用いて  $|f|< f_{sl}/2$  の制限する。H(z) の出力  $x_2(nT)$  を  $f_{sl}$  で標本化する,すなわち,L 個おきに間引くことにより  $x_2(nLT)$  を得る。フィルタ構成を図 7.17 に示し,周波数特性の変化を図 7.18 に示す。この場合は出力 1 サンプルを計算するのに必要な乗算回数は N 回であるが,出力

は 1 秒間に  $f_{sl}$  回の割で計算すればよいから計算量は約 1/L に低減される。

図 7.17 レート変換 (ダウンサンプリング)をフィルタ構成

図 7.18 レート変換 (ダウンサンプリング)における周波数特性の変化

# 〔3〕 有理数変換

レート変換の比率が有理数である場合も多い。  $f_{sh}/f_{sl}=L/K$  の場合を考える。 L , K は整数である。アップサンプリングにおける零内挿やダウンサンプリングにおける間引きはレート変換比率が整数倍でないと行えない。そこで, $f_{sl}$  と  $f_{sh}$  の間のレート変換はこれらの最小公倍数となる周波数  $f_{lcm}$  を介して行われる。  $f_{sl}\to f_{sh}$  の場合は  $f_{sl}\to (up)\to f_{lcm}\to (down)\to f_{sh}$  , $f_{sh}\to f_{sl}$  の場合は  $f_{sh}\to (up)\to f_{lcm}\to (down)\to f_{sl}$  となる。各々のアップサンプリング,ダウンサンプリングの過程は前述の方法と同じである。 $f_{lcm}$  で動作するフィルタの次数は高くなるが,1 秒間当たりの計算量はあまり増加しない。

# 〔4〕 応用例ディジタルオーディオオーバーサンプリング A/D 変換

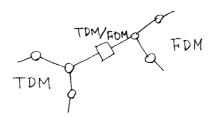

#### 7.3.2 **TDM/FDM** 変換

現在の電話回線網では図 7.19 に示すように,周波数分割多重 (Frequency Division Multiplex) 方式と時分割多重 (Time Division Multiplex) 方式が混在している。従って,これらの接続点では変換が必要である。この変換をベースバンドを介さないで,キャリアバンドで直接行う方法が TDM/FDM 変換である。

図 7.19 TDM と FDM が混在する電話回線網

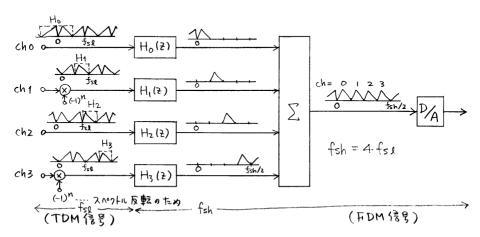

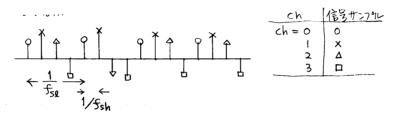

図 7.20 に TDM/FDM 変換のブロック図を示す。これは,4 チャネルの TDM 信号から 4 チャネルの FDM 信号にキャリアバンドで変換するものである。TDM 信号の波形を図 7.21 に示す。

図 7.20 TDM FDM 変換を行う過程

$ext{TDM}$  において, 各チャネルの標本化周波数は  $f_{sl}$  であり, 周波数領域では

図 7.21 TDM 信号の波形

ベースバンドに対応する。時分割多重された 4 チャネルに対する標本化周波数は  $f_{sh}=4f_{sl}$  である。従って,TDM における各チャネルの周波数特性は図 7.20の TDM 信号の箇所に示すようになる。 $(-1)^n$  はスペクトルの向きを反転するためのものである。TDM の各チャネルにおいて, $f_{sh}$  で動作する帯域制限フィルタ  $H_i(z)$  を通してキャリアバンドにおける成分を取り出す。これらを加算することにより FDM された信号を得る。 $H_i(z)$  は基本的にレート変換フィルタとなる。 $H_i(z)$  は FFT と  $f_{sl}$  で動作するフィルタ群で構成され計算量を大幅に低減できる。

# 7.4 演習問題

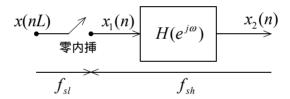

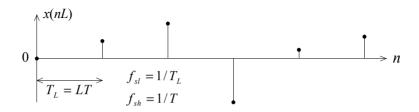

- 1. 標本化周波数の変換(アップサンプリング)に関して以下の問に答えよ.  $f_{sl}=1/T_L$  で標本化された信号を x(nL) とする.アップサンプル後の標本化周波数を  $f_{sh}=1/T, T=T_L/L$  とする.x(nL) を零内挿で L 倍にアップサンプルした信号を  $x_1(n)$  とし,これをフィルタ  $H(e^{j\omega})$  に通して得られる信号を  $x_2(n)$  とする.図 7.22 にプロック図,図 7.23 に x(nL) の波形,図 7.24 に x(nL) の周波数特性(フーリエ変換) $X(e^{j\omega})$  とフィルタ特性  $H(e^{j\omega})$  を示す.但し,L=3 である.

- (a)  $x_1(n)$ ,  $x_2(n)$  の周波数特性(フーリエ変換) $X_1(e^{j\omega})$ ,  $X_2(e^{j\omega})$  を  $0 \sim f_{sh}$  の範囲で図示せよ(別々の図にすること). 但し,振幅方向の変化は無視するものとする.

図 7.22 アップサンプルを行うブロック図

図 7.23 入力信号 x(nL) の波形

図 7.24 入力信号 x(nL) とフィルタの周波数特性

- (b)  $x_1(n)$ ,  $x_2(n)$  を図示せよ(別々の図にすること). 但し,x(nL) も同時に図示すること. $x_2(n)$  に関してはサンプル点 = nL 以外の点では概略図(大まかに内挿する)でよい.標本間隔(秒)を明示すること.

- (c) フィルタを N=90 タップ (乗算器の数=90) の直接形 FIR フィルタで構成した場合 , 1 秒間に必要な乗算回数と加算回数 ( = 乗算回数 1 ) を求めよ . 但し ,  $f_{sl}=8$ kHz とする .

- 2. 標本化周波数の変換(ダウンサンプル)に関して以下の問に答えよ. $f_{sh}$ で標本化された信号を x(n) とし,そのフーリエ変換を  $X(e^{j\omega})$  とする.x(n) をフィルタ  $H(e^{j\omega})$  に入力して得られる出力信号を  $x_1(n)$  とする.さらに, $x_1(n)$  を 1/L 倍にダウンサンプルして得られる信号を  $x_2(nL)$  とする.図 7.25 にプロック図,図 7.26 に x(n) の周波数特性(フーリエ変換) $X(e^{j\omega})$  とフィルタ特性  $H(e^{j\omega})$ ,図 7.23 に  $x_1(n)$  の波形を示す.但し,L=3 である.

図 7.25 ダウンサンプルを行うブロック図

- (a)  $x_1(n)$  と  $x_2(nL)$  の周波数特性(フーリエ変換)) $X_1(e^{j\omega})$ , $X_2(e^{j\omega})$ を  $0\sim f_{sh}$  の範囲で図示せよ(別々の図にすること).但し,振幅方向の変化は無視するものとする.

- (b)  $x_2(nL)$  を図示せよ、図 7.27 を参考にして概略図を示せ、標本間隔 (秒)を明示すること、

- (c) フィルタを N=90 タップ (乗算器の数=90) の直接形 FIR フィル

図 7.26 入力信号 x(n) とフィルタの周波数特性

図 7.27 フィルタの出力信号  $x_1(n)$  の波形

夕で構成した場合,1秒間に必要な乗算回数と加算回数(=乗算回 数 - 1)を求めよ.但し, $f_{sl}=8\mathrm{kHz}$ とする.